My simulation is complete! Woot!!! A couple key leanings. This was the first time in a long time I’ve worked with a netlist and I’ve never had to import subcircuts or models. gnetlist is an OK tool but it definitely does not support subcircuits very well or maybe there are some flags I did not enable for it to compile out of the schematic… So what I did is I used the call:

gnetlist -g spice-sdb -o RFID1.net RFID1.sch

This is documented in the gnetlist wiki so what it got me is as follows:

*******************************

* Begin .SUBCKT model *

* spice-sdb ver 4.28.2007 *

*******************************

.SUBCKT LM358

*vvvvvvvv Included SPICE model from ./models/bs170.mod vvvvvvvv

*ZETEX BS170 Mosfet Spice Subcircuit Last revision 12/85

*

.SUBCKT BS170 3 4 5

* D G S

M1 3 2 5 5 N3306M

RG 4 2 270

RL 3 5 1.2E8

D1 5 3 N3306D

.MODEL N3306M NMOS VTO=1.824 RS=1.572 RD=1.436 IS=1E-15 KP=.1233

+CGSO=28E-12 CGDO=3E-12 CBD=35E-12 PB=1

.MODEL N3306D D IS=5E-12 RS=.768

.ENDS BS170

*

* (C) 1991 ZETEX PLC

*

* The copyright in this model and the design embodied belong to

* Zetex PLC (“Zetex”). It is supplied free of charge by Zetex for

* the purpose of research and design and may be used or copied

* intact (including this notice) for that purpose only. All other

* rights are reserved. The model is believed accurate but no

* condition or warranty as to its merchantability or fitness for

* purpose is given and no liability in respect of any use is

* accepted by Zetex PLC, its distributors or agent.

*

*

* Zetex PLC, Fields New Road, Chadderton, Oldham OL9 8NP

*^^^^^^^^ End of included SPICE model from ./models/bs170.mod ^^^^^^^^

*

*vvvvvvvv Included SPICE model from ./models/bc547.mod vvvvvvvv

.MODEL BC547 NPN ( IS =1.8E-14 ISE=5.0E-14 NF =.9955 NE =1.46 BF =400

+BR =35.5 IKF=.14 IKR=.03 ISC=1.72E-13 NC =1.27 NR =1.005 RB =.56 RE =.6

+RC =.25 VAF=80 VAR=12.5 CJE=13E-12 TF =.64E-9 CJC=4E-12 TR =50.72E-9

+VJC=.54 MJC=.33 )

*^^^^^^^^ End of included SPICE model from ./models/bc547.mod ^^^^^^^^

*

*vvvvvvvv Included SPICE model from ./models/LM358.mod vvvvvvvv

*//////////////////////////////////////////////////////////////////////

* (C) National Semiconductor, Inc.

* Models developed and under copyright by:

* National Semiconductor, Inc.

*/////////////////////////////////////////////////////////////////////

* Legal Notice: This material is intended for free software support.

* The file may be copied, and distributed; however, reselling the

* material is illegal

*////////////////////////////////////////////////////////////////////

* For ordering or technical information on these models, contact:

* National Semiconductor’s Customer Response Center

* 7:00 A.M.–7:00 P.M. U.S. Central Time

* (800) 272-9959

* For Applications support, contact the Internet address:

* amps-apps@galaxy.nsc.com

*//////////////////////////////////////////////////////////

*LM358 DUAL OPERATIONAL AMPLIFIER MACRO-MODEL

*//////////////////////////////////////////////////////////

*

* connections: non-inverting input

* | inverting input

* | | positive power supply

* | | | negative power supply

* | | | | output

* | | | | |

* | | | | |

.SUBCKT LM358 1 2 99 50 28

*

*Features:

*Eliminates need for dual supplies

*Large DC voltage gain = 100dB

*High bandwidth = 1MHz

*Low input offset voltage = 2mV

*Wide supply range = +-1.5V to +-16V

*

*NOTE: Model is for single device only and simulated

* supply current is 1/2 of total device current.

* Output crossover distortion with dual supplies

* is not modeled.

*

****************INPUT STAGE**************

*

IOS 2 1 5N

*^Input offset current

R1 1 3 500K

R2 3 2 500K

I1 99 4 100U

R3 5 50 517

R4 6 50 517

Q1 5 2 4 QX

Q2 6 7 4 QX

*Fp2=1.2 MHz

C4 5 6 128.27P

*

***********COMMON MODE EFFECT***********

*

I2 99 50 75U

*^Quiescent supply current

EOS 7 1 POLY(1) 16 49 2E-3 1

*Input offset voltage.^

R8 99 49 60K

R9 49 50 60K

*

*********OUTPUT VOLTAGE LIMITING********

V2 99 8 1.63

D1 9 8 DX

D2 10 9 DX

V3 10 50 .635

*

**************SECOND STAGE**************

*

EH 99 98 99 49 1

G1 98 9 POLY(1) 5 6 0 9.8772E-4 0 .3459

*Fp1=7.86 Hz

R5 98 9 101.2433MEG

C3 98 9 200P

*

***************POLE STAGE***************

*

*Fp=2 MHz

G3 98 15 9 49 1E-6

R12 98 15 1MEG

C5 98 15 7.9577E-14

*

*********COMMON-MODE ZERO STAGE*********

*

*Fpcm=10 KHz

G4 98 16 3 49 5.6234E-8

L2 98 17 15.9M

R13 17 16 1K

*

**************OUTPUT STAGE**************

*

F6 50 99 POLY(1) V6 300U 1

E1 99 23 99 15 1

R16 24 23 17.5

D5 26 24 DX

V6 26 22 .63V

R17 23 25 17.5

D6 25 27 DX

V7 22 27 .63V

V5 22 21 0.27V

D4 21 15 DX

V4 20 22 0.27V

D3 15 20 DX

L3 22 28 500P

RL3 22 28 100K

*

***************MODELS USED**************

*

.MODEL DX D(IS=1E-15)

.MODEL QX PNP(BF=1.111E3)

*

.ENDS

*$

*^^^^^^^^ End of included SPICE model from ./models/LM358.mod ^^^^^^^^

*

*============== Begin SPICE netlist of main design ============

R12 0 8 50

R11 0 5 50

Vin 1 0 pulse 0 3.3 125kHz

Q2 0 7 6 BC547

XU2 8 12 6 0 +5V LM358

XU1 5 12 4 0 +5V LM358

Q1 0 2 9 BS170

D1 10 11 1N4148

R10 0 12 1k

R9 12 +5V 4k

L1 10 9 10NH

R5 0 11 270k

C1 11 3 12NF

C3 0 11 4NF

C2 0 10 1NF

R1 9 +5V 100

R7 6 8 100k

R6 7 5 1k

R8 6 +5V 33k

R3 4 5 390k

R4 4 3 33k

R2 2 1 1K

.ends LM358

*******************************

This is impossible to parse for kjwaves so I had to trim it to this version:

*============== Begin SPICE netlist of main design ============

*form PULSE(V1 V2 TD TR TF PW PER)

Vin 1 0 PULSE(0 5V 0 8ns 8ns 0.004ms 0.008ms) dc=0

Q2 0 7 6 BC547

XU2 8 12 6 0 +5V LM358

XU1 5 12 4 0 +5V LM358

XQ1 0 2 9 BS170

XD1 10 11 1N4148

R10 0 12 1k

R9 12 +5V 4k

L1 10 9 0.37MH

R5 0 11 270k

C1 11 3 12NF

C3 0 11 4NF

C2 0 10 1NF

R1 9 +5V 100

R7 6 8 100k

R6 7 5 1k

R8 6 +5V 33k

R3 4 5 390k

R4 4 3 33k

R2 2 1 1K

.MODEL BC547 NPN ( IS =1.8E-14 ISE=5.0E-14 NF =.9955 NE =1.46 BF =400

+BR =35.5 IKF=.14 IKR=.03 ISC=1.72E-13 NC =1.27 NR =1.005 RB =.56 RE =.6

+RC =.25 VAF=80 VAR=12.5 CJE=13E-12 TF =.64E-9 CJC=4E-12 TR =50.72E-9

+VJC=.54 MJC=.33 )

.include /home/shane/Documents/Design/models/bs170.mod

.include /home/shane/Documents/Design/models/LM358.mod

.include /home/shane/Documents/Design/models/1N4148.prm

.opt acct list node

.tran 8ns .08ms

.end

Notice the ‘X’ next to the component calls. This indicates the subcircuit model identified by the .include line. 🙂

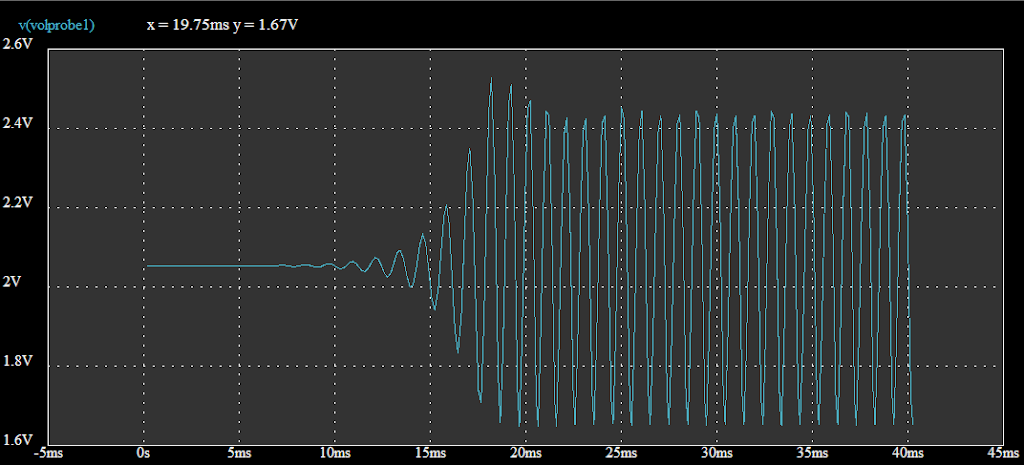

This loaded and ran in kjwaves and gave what I believe are reasonable results. They are definitely NOT what the author describes should be the result but I think that it is something a micro-controller can read in and change to a cmos logic signal.